# In-situ RHEED and characterization of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics

## In-situ RHEED and characterization of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics

R.G. Bankras

The graduation committee consists of:

chair: prof.dr.ir. J. van Amerongen University of Twente secretary: prof.dr.ir. A.J. Mouthaan University of Twente promoter: prof.dr. J. Schmitz University of Twente asst. promoter: dr. J. Holleman University of Twente University of Twente Philips Research Eindhoven

members: prof.dr. L.K. Nanver Delft University of

Technology

prof.dr.ing. D.H.A. Blank University of Twente prof.dr.ir. B. Poelsema University of Twente prof.dr.ir. R.A.M. Wolters University of Twente

This research was supported by Dutch Technology Foundation STW ("High-κ dielectric material for MOS gate dielectrics", TMF 5379) and carried out in the Semiconductor Components group, MESA<sup>+</sup> Institute for Nanotechnology, University of Twente, the Netherlands.

University of Twente P.O. Box 217, 7500 AE Enschede, the Netherlands info@utwente.nl http://www.utwente.nl/

MESA<sup>+</sup> Institute for Nanotechnology P.O. Box 217, 7500 AE Enschede, the Netherlands info@mesaplus.utwente.nl http://www.mesaplus.utwente.nl/

Dutch Technology Foundation STW P.O. Box 3021, 3502 GA Utrecht, the Netherlands info@stw.nl http://www.stw.nl/

Keywords: atomic layer deposition (ALD), high- $\kappa$  dielectrics, reflection high-energy electron diffraction (RHEED), aluminum oxide (Al<sub>2</sub>O<sub>3</sub>).

Title: In-situ RHEED and characterization of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics

Author: ir. R.G. Bankras (radko@bankras.net)

ISBN-10: 90-365-2271-4 ISBN-13: 978-90-365-2271-7

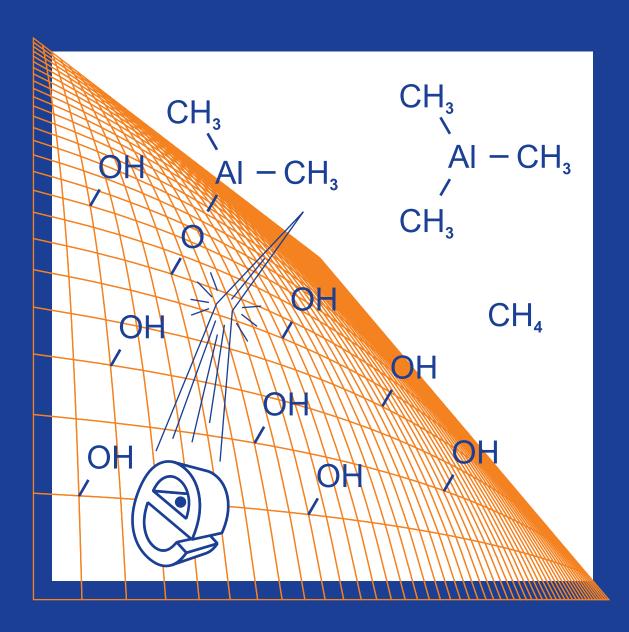

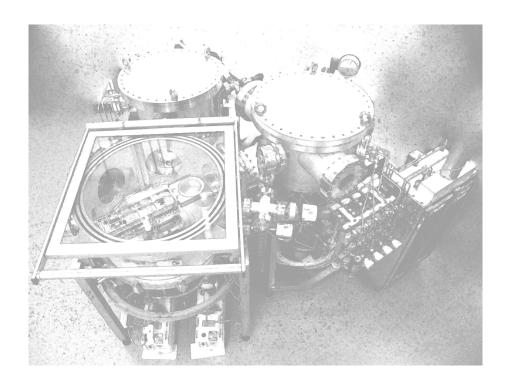

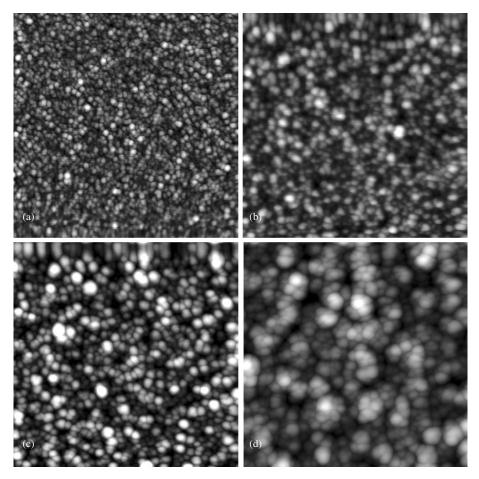

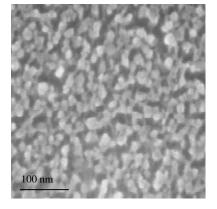

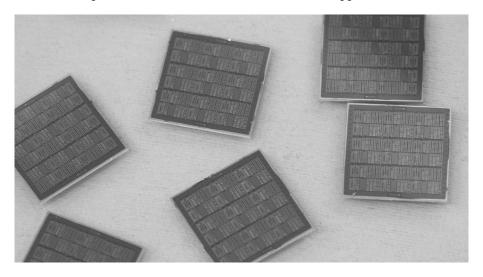

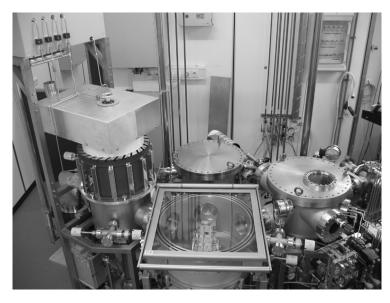

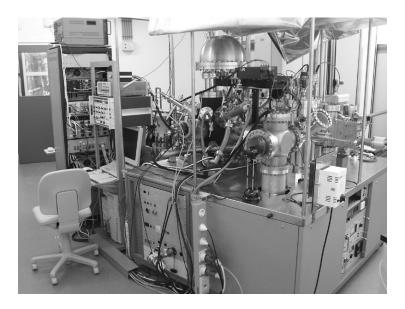

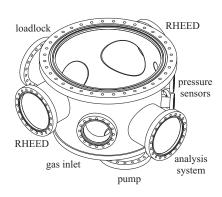

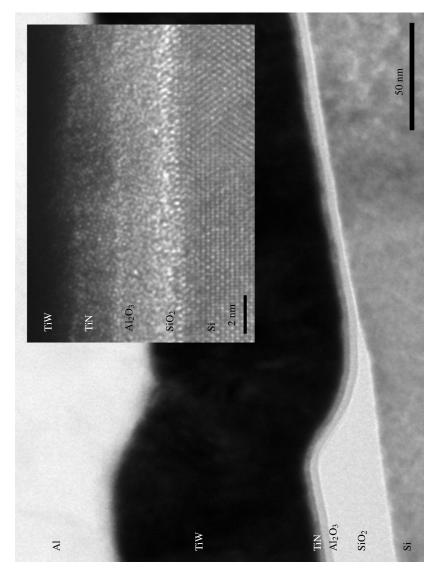

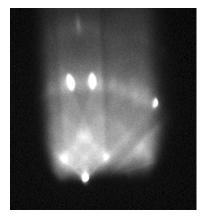

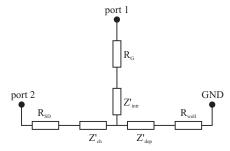

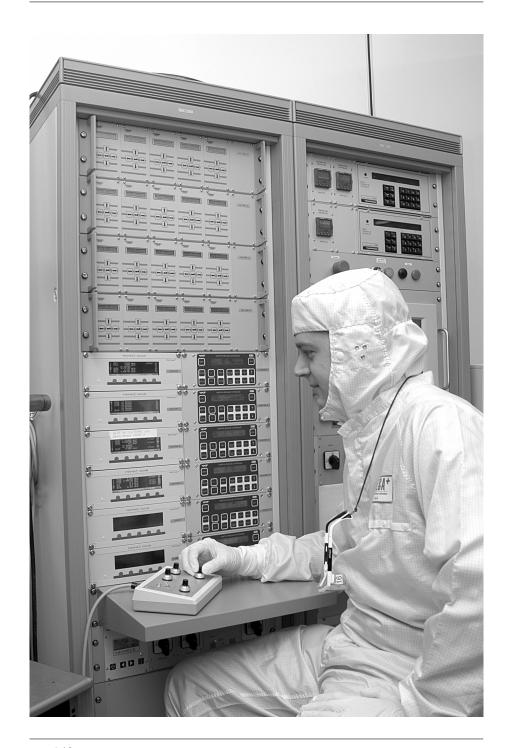

Cover: illustration of in-situ RHEED during atomic layer deposition of  $Al_2O_3$  (front side); the Semiconductor Components part of the cluster system and a finished silicon wafer with test structures for characterization of the ALD  $Al_2O_3$ /TiN gate stack (back side).

#### Copyright © 2006 by Radko Bankras, Enschede, the Netherlands

All rights reserved. Subject to exceptions provided for by law, no part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of the copyright owner. No part of this publication may be adapted in whole or in part without the prior written permission of the author.

This document was typeset using LATEX  $2\varepsilon$  on October 5th, 2006.

Printing office: PrintPartners Ipskamp B.V., Enschede, the Netherlands

## In-situ RHEED and characterization of ALD $AL_2O_3$ gate dielectrics

#### DISSERTATION

to obtain

the doctor's degree at the University of Twente,

on the authority of the rector magnificus,

prof.dr. W.H.M. Zijm,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday, November 1st 2006 at 13:15

by

Radko Gerard Bankras born on November 30th 1975 in Bovenkarspel, the Netherlands This dissertation is approved by the promoter prof.dr. J. Schmitz and the assistant promoter dr. J. Holleman. To my parents, Jacques and Mia Bankras, for their support and encouragement.

## Contents

| In | trodu | uction                                           | 1  |

|----|-------|--------------------------------------------------|----|

|    | Refe  | erences                                          | 3  |

| Ι  | Bac   | kground                                          | 5  |

| 1  | Gate  | e dielectrics                                    | 7  |

|    | 1.1   | Technology development                           | 7  |

|    | 1.2   | High dielectric constant materials               | 8  |

|    |       | 1.2.1 Polarizability and (relative) permittivity | 9  |

|    |       |                                                  | 11 |

|    |       |                                                  | 15 |

|    |       |                                                  | 16 |

|    | 1.3   |                                                  | 22 |

|    |       |                                                  | 22 |

|    |       |                                                  | 23 |

|    | 1.4   |                                                  | 24 |

|    | 1.5   |                                                  | 25 |

|    | Refe  |                                                  | 25 |

| 2  | Puls  | sed laser deposition                             | 29 |

|    | 2.1   | Introduction                                     | 29 |

|    | 2.2   |                                                  | 31 |

|    | 2.3   |                                                  | 35 |

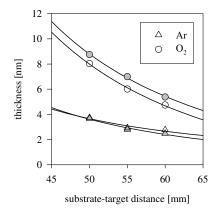

|    |       | 2.3.1 Thickness                                  | 36 |

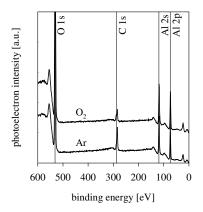

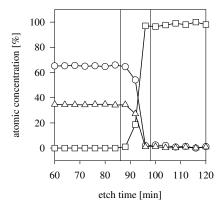

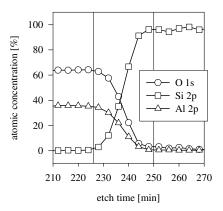

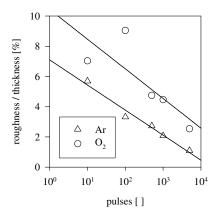

|     | 2.4<br>2.5<br>2.6<br>Refe | 2.3.2 Composition  2.3.3 Surface morphology  Characterization of devices  Interface stability  Conclusions  rences | 37<br>40<br>41<br>44<br>47<br>47 |

|-----|---------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------|

| II  | Exp                       | perimental                                                                                                         | 49                               |

| 3   | Aton                      | nic layer deposition                                                                                               | 51                               |

|     | 3.1                       | Introduction                                                                                                       | 51                               |

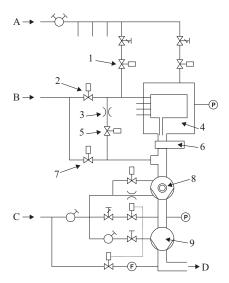

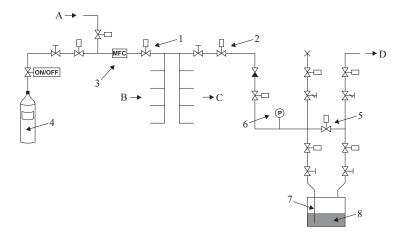

|     | 3.2                       | Design of the ALD system                                                                                           | 54                               |

|     |                           | 3.2.1 ALD process chamber                                                                                          | 56                               |

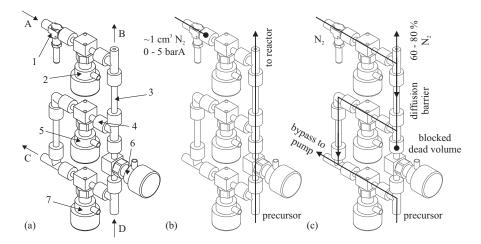

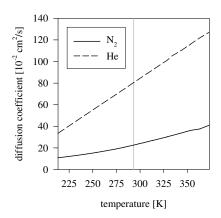

|     |                           | 3.2.2 Precursor handling                                                                                           | 59                               |

|     | 3.3                       | Characterization of the reactor                                                                                    | 63                               |

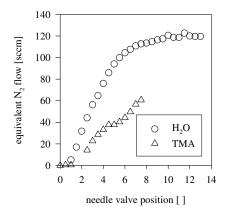

|     |                           | 3.3.1 Gas flow and pump capacity                                                                                   | 63                               |

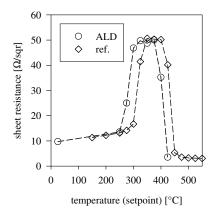

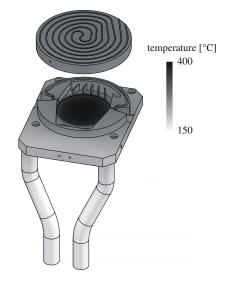

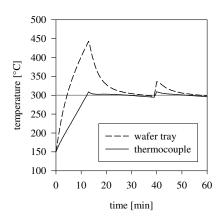

|     |                           | 3.3.2 Deposition temperature                                                                                       | 65                               |

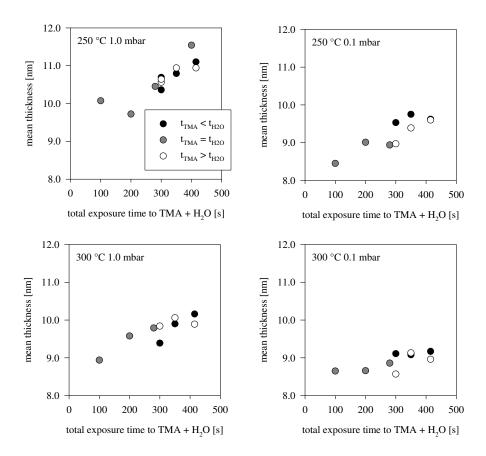

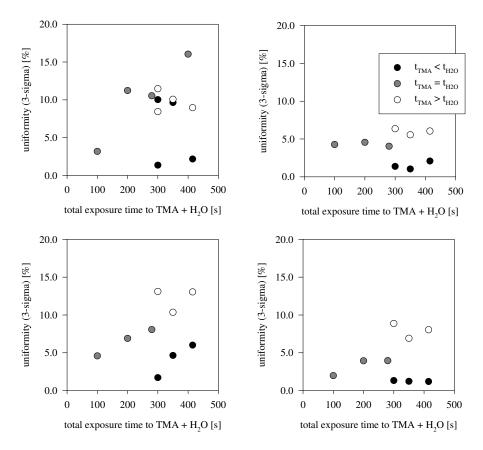

|     |                           | 3.3.3 Uniformity                                                                                                   | 68                               |

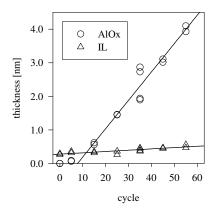

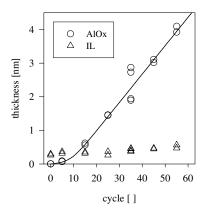

|     | 3.4                       | Characterization of thin films                                                                                     | 73                               |

|     | 3.5                       | Conclusions                                                                                                        | 78                               |

|     | Refe                      | rences                                                                                                             | 79                               |

| III | I De                      | evelopment                                                                                                         | 81                               |

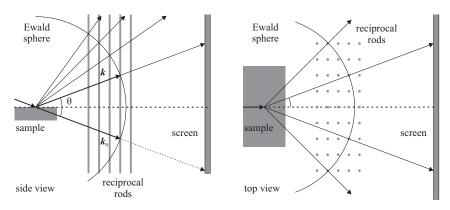

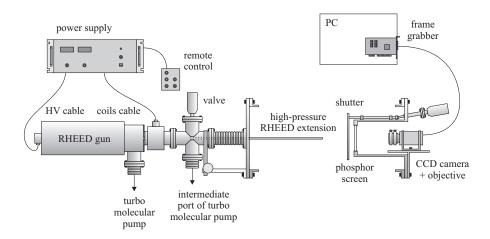

| 4   | Elec                      | tron reflection                                                                                                    | 83                               |

|     | 4.1                       | Introduction                                                                                                       | 83                               |

|     | 4.2                       | Electron-atom interactions                                                                                         | 85                               |

|     |                           | 4.2.1 Scattering potential                                                                                         | 85                               |

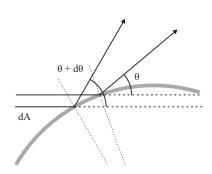

|     |                           | 4.2.2 Elastic scattering                                                                                           | 86                               |

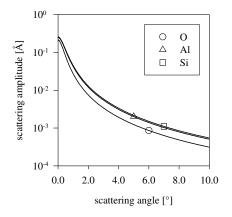

|     |                           | 4.2.3 Scattering amplitude                                                                                         | 87                               |

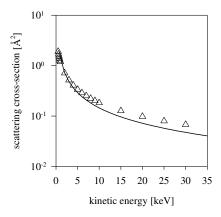

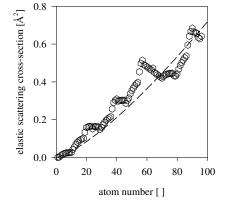

|     |                           | 4.2.4 Scattering cross-section                                                                                     | 88                               |

|     | 4.3                       | Electron-solid interactions                                                                                        | 91                               |

|     |                           | 4.3.1 Crystal lattice                                                                                              | 92                               |

|     |                           | 4.3.2 RHEED intensity                                                                                              | 93                               |

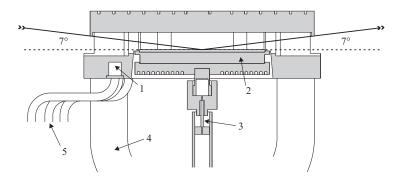

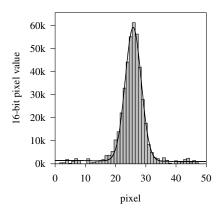

|     | 4.4                       | RHEED setup and data analysis                                                                                      | 94                               |

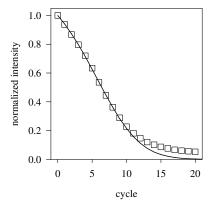

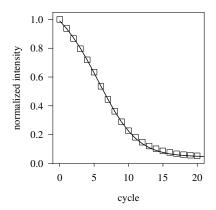

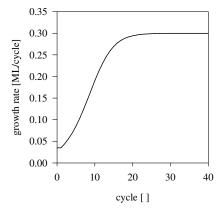

|     | 4.5                       | Measurement results                                                                                                | 99                               |

|     | 4.6                       | Conclusions                                                                                                        | 101                              |

|     | Refe                                    | rences                     | 101                                    |

|-----|-----------------------------------------|----------------------------|----------------------------------------|

| 6   | 5.1<br>5.2<br>5.3<br>5.4<br>Refe        | Introduction               | 105<br>105<br>106<br>109<br>114<br>115 |

|     | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Refe | Introduction               | 121<br>124<br>128                      |

| IV  | C                                       | osing                      | 131                                    |

| 7   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5         | Clusions Summary           | 133<br>133<br>134<br>135<br>136<br>137 |

| Sa  | menv                                    | atting (abstract in Dutch) | 139                                    |

| Ac  | knov                                    | ledgements                 | 141                                    |

| Bio | ograp                                   | hy                         | 147                                    |

| Aŗ  | pen                                     | lix                        | 149                                    |

| A   | Diff                                    | usion barrier              | 151                                    |

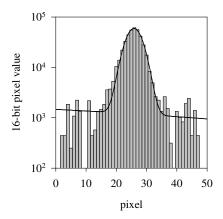

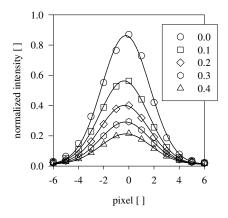

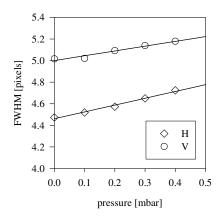

| В   | Gau                                     | ssian fit                  | 153                                    |

## In-situ RHEED and characterization of ALD $Al_2O_3$ gate dielectrics

| C Process flow  | 155 |

|-----------------|-----|

| List of symbols | 165 |

| Index           | 169 |

## Introduction

The books used in the (electrical) engineering curriculum usually have titles that start with "Introduction to ..." or "First principles of ...". This observation is easily followed by a question about the use of books on matter of importance. However, after graduation the student is deployed in the experimental field of the unknown and not-yet-known. Progress in engineering has led to some fundamental boundaries of basic principles. The infinite urge of scientific progress now requires solutions, which can not (yet) be found in textbooks.

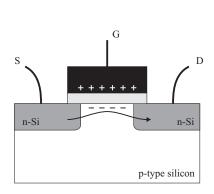

The introduction of personal computers in the late seventies and early eighties of the twentieth century can be seen as the start of the digital era for consumers. For several years, the massive electronic calculators could only be afforded and operated by large companies and universities. [0.1] The ability to perform vast amounts of effortless calculations is attributed to the invention of the transistor in 1947 by W.B. Shockley, J. Bardeen and W.H. Brattain. [0.2] The novel solid state electronic switch was eventually developed into the first MOSFET, or metal oxide semiconductor field effect transistor. Nowadays, the MOSFET still forms the basis of most products of the multibillion dollar semiconductor industry.

The success of the semiconductor industry has been its ability to engineer single transistors into ever more complex integrated circuits. [0.3] Manufacturing highly valued products from a minimum amount of material, drove the development of advanced semiconductor technologies. The downscaling trend

of semiconductors is a balancing act, in which expensive new technologies have to be approved by additional profit from being able to manufacture more products per wafer. "Last year, more transistors were produced - and at lower cost - than grains of rice". [0.4] However, after five decades of downscaling, some fundamental limits have been reached.

Figure 1: schematic cross-section of a field effect transistor, with source (S), gate (G) and drain (D) connections. The gate oxide is light gray colored and isolates the gate (black) from the silicon substrate.

**Figure 2:** analogue of a MOSFET transistor: the flow from source to drain is controlled by a gate, which for the best result should only be positioned in fully opened (or closed) state.

The field effect transistor can be opened (or closed) due to a counter charge of the gate potential in the semiconductor. The amount of charge depends on the applied gate bias and the dielectric properties of the isolation material between gate and substrate. This gate oxide has followed the down-scaling trend up to thicknesses of only a few atomic layers. Unfortunately, leakage currents through the gate oxide have increased exponentially with the reduction of oxide thickness and have now become unacceptable.

The aim of the research, as presented in this dissertation, is to contribute to the development of a replacement gate dielectric. The approach was to study the initial growth of high- $\kappa$  metal oxides in an ultra-clean (high vacuum) atomic layer deposition technology by in-situ characterization. One of the most studied high- $\kappa$  dielectric materials is aluminum oxide and is often used as example material for gate oxide replacement. Hence the title of this dissertation "In-situ RHEED and characterization of ALD Al<sub>2</sub>O<sub>3</sub> gate dielectrics".

In chapter 1 all relevant aspects of gate dielectrics will be discussed. The information provided in this chapter should form a base for the experimental work on pulsed laser deposition (PLD) and atomic layer deposition (ALD), as presented in chapters 2 and 3, respectively. Both deposition techniques have been used to deposit Al<sub>2</sub>O<sub>3</sub> gate dielectrics. Chapter 4 discusses the use of an in-situ characterization technique in an atomic layer deposition reactor, which is commonly used in pulsed laser deposition systems: reflection high-energy electron diffraction (RHEED). The chapter presents the implementation of the RHEED technique in the ALD reactor and the results obtained from measurements during Al<sub>2</sub>O<sub>3</sub> deposition. The results from modeling RHEED during ALD growth, used to interpret the results obtained in chapter 4, will be discussed in chapter 5. Chapter 6 presents the high frequency electrical characterization of Al<sub>2</sub>O<sub>3</sub> gate dielectrics in a special test structure. Finally, a summary of results, the conclusions of this dissertation, the original contributions of this work and recommendations for further research can all be found in chapter 7.

This project has been a collaboration between the chairs of Semiconductor Components and Solid State Physics of the University of Twente. The project was supported by Dutch Technology Foundation STW (TMF5379, "High- $\kappa$  dielectric material for MOS gate dielectrics"). The users' committee consisted of Philips Research and ASM International representatives.

#### References

- [0.1] Computer History Museum, *Timeline 1945 to 1990*, available online, http://www.computerhistory.org/, 2004.

- [0.2] Riordan M. and Hoddeson L., Crystal Fire: The invention of the transistor and the birth of the information age, W.W. Norton & Company, New York, 1997.

- [0.3] Intel Corp., Intel Museum, available online, http://www.intel.com/, 2006.

- [0.4] Semiconductor Industry Association, Annual report 2005, available online, http://www.sia-online.org/, 2005.

| In-situ RHEED and characterization of ALD Al <sub>2</sub> O <sub>3</sub> gate dielectrics |  |

|-------------------------------------------------------------------------------------------|--|

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

|                                                                                           |  |

# Part I Background

## 1

## Gate dielectrics

The use of integrated circuits (or chips) has increased for several decades at an incredible rate. Nowadays almost every household appliance is digitally controlled and contains functionality beyond the grasp of most users. However, the customer still demands electronic devices to be smaller, operate faster, have increased capabilities, be more reliable and use less energy. In order to answer to the customer's requests, (or actually to be able to satisfy the customer with a new product before industrial competitors advance), circuit designers have been taking advantage of every bit of improvement in the integrated circuit technology.

## 1.1 Technology development

Since the first use of metal oxide semiconductor (MOS) transistors in the early 1960s, the manufacturing process has been improved up to a highly advanced semiconductor technology. The ability to scale transistors to decreasing dimensions has resulted in higher performances and made CMOS architecture the dominant technology in current integrated circuits. This downscaling trend, as described by Moore's law, has reduced MOS gate dimensions from 10  $\mu m$  in 1970 to a present day size of less than 0.1  $\mu m$ .

For decades silicon dioxide has been used as the gate dielectric material for standard MOS technology. One of the problems with scaling MOSFETs beyond the 0.1 µm technology, is the increasing leakage current through the gate dielectric. The traditional SiO<sub>2</sub> gate dielectric will reach fundamental scaling limits near the effective electrical thickness of only a few molecular

layers. The International Technology Roadmap for Semiconductors (ITRS) indicates that the rate of device scaling would produce 45 nm generation devices using equivalent gate oxide thicknesses (EOT) of 0.7 nm in 2010 (see table 1.1). To enable MOS scaling in the future, solutions will have to be found and the semiconductor technology will have to be altered.

| year   | DRAM           | physical equivalent  |

|--------|----------------|----------------------|

|        | 1/2 pitch [nm] | oxide thickness [nm] |

| 2000*  | 165            | 1.9-2.5              |

| 2002*  | 130            | 1.5-1.9              |

| 2004   | 90             | 1.2                  |

| 2006   | 70             | 1.0                  |

| 2007   | 65             | 0.9                  |

| 2008   | 57             | 0.8                  |

| 2010   | 45             | 0.7                  |

| 2013   | 32             | 0.6                  |

| 2016   | 22             | 0.5                  |

| 2018** | 18             | 0.5                  |

| 2020** | 14             | 0.5                  |

**Table 1.1:** technology development in ITRS editions [1.1] of 1999/2000(\*), 2003/2004 and 2005(\*\*), displayed as DRAM ½ pitch design dimensions and physical equivalent oxide thickness of transistors in microprocessor units.

## 1.2 High dielectric constant materials

The typical leakage current of  $SiO_2$ , at a gate bias of 1 V, changes from  $10^{-12}$  A/cm<sup>2</sup> at 3.5 nm to 10 A/cm<sup>2</sup> at 1.5 nm. [1.2] The leakage current density of future generation CMOS devices is forecast to exceed 1 kA/cm<sup>2</sup>. [1.1] For use in low-power applications, the leakage current of the gate dielectric has to be less than  $10^{-3}$  A/cm<sup>2</sup>. [1.3] A solution could be found in replacement of the traditional thermally grown silicon dioxide, by deposition of an alternative material with a higher relative permittivity ( $\kappa$ ). However, this will only (temporarily) solve one of the barriers that are limiting future development of the CMOS technology. Related to the search for a suitable high- $\kappa$  dielectric material are the research of different starting materials (substrates), low- $\kappa$  materials for interconnect dielectrics and alternative gate electrode metals. The question is for how long an advanced technology can be improved and when the semiconductor industry starts the development of new technologies to replace CMOS technology.

### 1.2.1 Polarizability and (relative) permittivity

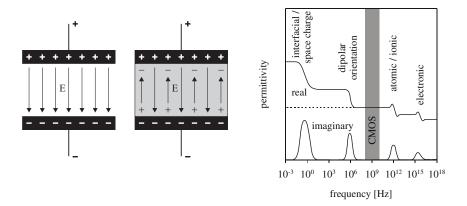

In order to determine which dielectric materials are suitable for high- $\kappa$  gate oxide application, a detailed understanding is required of how different materials affect an electric field. The electric field is formed between two isolated metal plates (the gate and the substrate) with a potential difference, e.g. when a positive charge is applied to the gate. This electric field is directed from the positively charged plate to the negatively countercharged plate as drawn in figure 1.1 and is given by

$$E = \frac{Q}{\varepsilon_0 \cdot d},\tag{1.1}$$

where Q is the charge per unit area on a plate, d the distance between the plates and  $\varepsilon_0$  the permittivity of free space.

**Figure 1.1:** electric field between two charged metal plates in free space and in a dielectric material.

**Figure 1.2:** frequency dependence of the real  $\varepsilon'$  and imaginary  $\varepsilon''$  parts of the dielectric permittivity. [1.4]

When the medium between the two metal plates is a polarizable dielectric material, the electric field is reduced by an internal counterfield. This internal electric field is the result of the interaction between the applied charges and bound charges in the dielectric material. A negative charge is attracted (displaced) towards the positive plate and vice verse. The orientation of (polarization) charges in the dielectric material is possible by different polarization mechanisms of the material. The actual electric field is the sum (subtraction)

of both electric fields and is calculated by

$$E = \frac{Q}{\kappa \cdot \varepsilon_0 \cdot d}.\tag{1.2}$$

The permittivity of a material is a measure of the interaction between an electric field and the material. Equation 1.3 [1.5] shows the relation between displacement D, electric field E and polarization P

$$D = \varepsilon_0 \cdot E + P = \varepsilon_0 \cdot (1 + \chi_e) \cdot E = \kappa \cdot \varepsilon_0 \cdot E, \tag{1.3}$$

in which  $\chi_e$  is the electronic susceptibility of the material. The commonly used term dielectric constant is the permittivity of a material, normalized to the permittivity of free space  $\epsilon_0$ . A list of symbols used in this dissertation can be found on page 165.

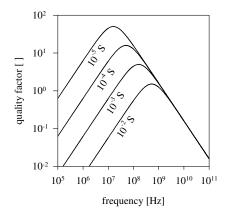

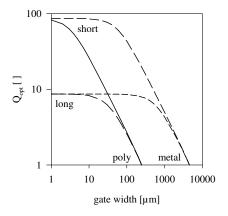

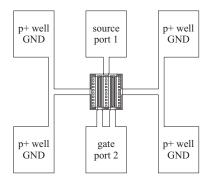

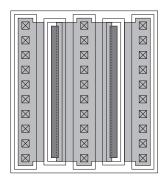

Figure 1.2 shows how the different polarization mechanisms, that make up the permittivity of the material, are lost at elevated frequencies of the applied external bias. Electronic polarization is a shift of the electron cloud of an atom from its center position. The average distance between the negative electron cloud and positive nucleus forms a small electric field. Atomic or ionic polarization (distortion polarization) is the displacement of the negatively charged cations and positively charged anions that form the molecule. [1.6] A third contributing component is orientational polarization by alignment of permanent dipolar molecules. In principle all components can contribute to formation of a steady state internal electric field. Thus, the dielectric constant of a material depends on the frequency of the applied potential difference. Some polarization mechanisms (e.g. dipolar orientation) may be very weak or not present at all in the dielectric material, as visualized by the dashed line in figure 1.2. The imaginary part of the complex permittivity is the dielectric loss due to out-of-phase polarization and ohmic loss due to free charge carriers in the dielectric. The loss tangent  $tan(\delta)$  is the ratio between imaginary  $\epsilon''$  and real  $\varepsilon'$  parts of the permittivity and therefore one measure for the dielectric quality of a material

$$\tan(\delta) = \frac{\epsilon''}{\epsilon'} \ll 1. \tag{1.4}$$

In the frequency range of CMOS applications, 100 MHz - 10 GHz, only atomic/ionic and electronic polarization are able to contribute to the permittivity. The frequency dependence of the dielectric constant is often omitted in publications. The relation of the relative permittivity as squared refractive index, is only valid at optical frequencies. The dielectric constant at CMOS frequencies is higher, due to the contribution of atomic polarization.

### 1.2.2 Charge tunneling mechanisms

Thus, permittivity is an indication of the electrical charge a material is able to store. A material with higher permittivity is able to store more charge than a material with lower permittivity. The amount of charge is limited by the dielectric strength, which is the maximum electric field the dielectric material can withstand without breakdown. [1.5] Dielectric breakdown occurs when electrons are pulled from the molecules due to the large electric field. The free electrons accelerate and collide with other atoms. The result is an avalanche effect of ionization (due to collisions), the creation of permanent dislocations and possibly a conducting path between gate and substrate.

At lower electric fields, charge transport between the gate and the substrate is still possible and not even necessarily destructive or a reliability issue. The isolating properties of a dielectric material are the result of the relatively large (but not infinite) energy bandgap. The energy bandgap is the energy required to change an electron from a nonconducting (bound) state to a conducting (free) state. More important is the alignment of the energy bandgap to the energy levels of charge carriers in adjacent materials.

For electron transport from the semiconductor to the gate, the barrier height is the conduction band offset  $\Delta E_{\rm C}$ . The barrier height for electrons from the metal gate,  $\Phi_{\rm B}$ , is defined as the difference between the Fermi level in the gate and the conduction band level of the dielectric. The difference between both barriers is the electron affinity of the substrate  $\chi$  and the metal workfunction  $\Phi_{\rm M}$  of the gate

$$\Delta E_{\rm C} = q \cdot (\chi + \Phi_{\rm B} - \Phi_{\rm M}). \tag{1.5}$$

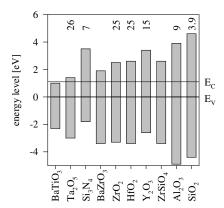

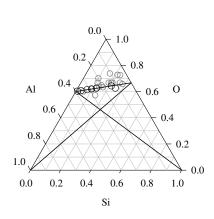

Figure 1.3 shows the energy bandgaps and their offsets with respect to a silicon substrate, of several high- $\kappa$  materials and silicon oxide. Aluminum oxide has only a dielectric constant of about 9, but also the highest bandgap of all high- $\kappa$  materials. Ludeke [1.8] obtained an Al<sub>2</sub>O<sub>3</sub>/Si conduction band offset of  $\Delta E_{\rm C} = 2.78$  eV. Obviously, the barrier height and energy bandgap should be included in the selection of a new dielectric material.

Several mechanisms enable electrons to overcome the energy barrier of the dielectric, either by gaining sufficient energy or by lowering of the energy barrier. Electrons gain energy from for example thermal excitation (phonons) or in an electric field. The required energy is reduced by intermediate energy trap levels (caused by defects in the dielectric) or an applied electric field, resulting in an effective lowering of the energy barrier. The so-called Frenkel-Poole emission is the field-enhanced electron emission from a trap level to the

**Figure 1.3:** bandgap offset of different high- $\kappa$  dielectrics, with respect to the conduction band and valence band energy levels of the silicon substrate. [1.7] The dielectric constant is displayed at the top of the bar.

lowered conduction band level. Although numerous other charge tunneling mechanisms have been published [1.9], the Fowler-Nordheim, Frenkel-Poole and direct tunneling mechanisms are most commonly used to describe leakage currents.

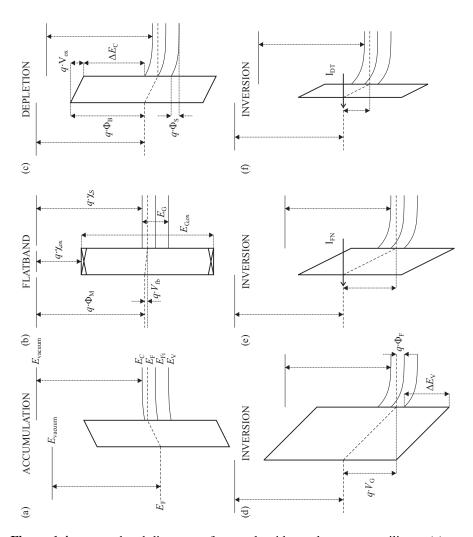

Under sufficiently high electric fields, electrons can tunnel through a very thin dielectric layer by the Fowler-Nordheim tunneling mechanism. The increase in Fermi level in the gate, changes the barrier height of the oxide to a triangular shape (see figure 1.4). The reduction of the effective oxide thickness results in the Fowler-Nordheim tunneling current density

$$I_{\rm FN} = A \cdot E_{\rm ox}^2 \cdot \exp\left(\frac{-B}{E_{\rm ox}}\right),$$

(1.6)

with

$$\begin{split} A &= \frac{q^3}{8\pi \cdot h \cdot \Phi_{\mathrm{B}} \cdot m^*}, \\ B &= \frac{8\pi}{3q \cdot h} \sqrt{2m^* \cdot m \cdot \Phi_{\mathrm{B}}{}^3}, \end{split}$$

where  $m^*$  is the relative effective mass of electrons in the dielectric. [1.10] The value and description of the other symbols can be found in the table on page 165.

**Figure 1.4:** energy band diagrams of a metal oxide stack on n-type silicon: (a) accumulation, (b) flatband conditions, (c) depletion, (d) inversion (thick oxides), (e) inversion (Fowler-Nordheim tunneling) and (f) inversion (direct tunneling).

Electrons can also tunnel directly through the full oxide thickness of thin dielectric layers. The direct tunneling mechanism dominates at low gate voltages in thin dielectric layers. The current density of the direct tunneling process is (in strong accumulation) approximately [1.11]

$$I_{\rm DT} = \frac{A \cdot E_{\rm ox}^2}{\left(1 - \sqrt{1 - \frac{q \cdot V_{\rm ox}}{\Phi_{\rm B}}}\right)^2} \cdot \exp\left(\frac{-B}{E_{\rm ox}} \cdot \left[1 - \left(1 - \frac{q \cdot V_{\rm ox}}{\Phi_{\rm B}}\right)^{3/2}\right]\right). \quad (1.7)$$

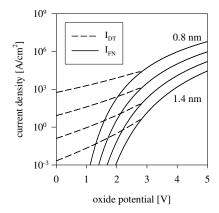

Figures 1.5 and 1.6 show the calculated tunneling current densities according to the direct and Fowler-Nordheim mechanisms (equations 1.6 and 1.7), for 0.8 - 1.4 nm  $SiO_2$  and  $Al_2O_3$ , respectively.

**Figure 1.5:** direct and Fowler-Nordheim tunneling current densities in 0.8 nm, 1.0 nm, 1.2 nm and 1.4 nm  $SiO_2$ , with barrier height  $\Phi_B = 3.5$  eV and relative effective electron mass m\* = 0.26.

**Figure 1.6:** tunneling current densities in 0.8 nm, 1.0 nm, 1.2 nm and 1.4 nm equivalent oxide thickness  $Al_2O_3$ , with barrier height  $\Phi_B = 2.8$  eV and relative effective electron mass  $m^* = 0.23$ .

The interface of silicon substrate and gate dielectric usually consists of a mixture of both materials or sometimes even a different material. A material with different properties can also be present at the interface between gate dielectric and gate electrode. The dielectric layer therefore actually consists of up to three capacitors in series

$$\frac{1}{C_{\text{dielectric stack}}} = \frac{1}{C_{\text{lower interface}}} + \frac{1}{C_{\text{bulk oxide}}} + \frac{1}{C_{\text{upper interface}}}.$$

(1.8)

This stack of dielectric materials could be engineered to have a high dielectric constant bulk and a high barrier height at the interface to reduce charge tunneling. Advanced gate stack engineering could lead towards laminated structures of different dielectric materials.

#### 1.2.3 Downscaling gate dielectrics

The higher dielectric constant of a new gate oxide will allow the use of a physically thicker layer, without a reduction in the gate capacitance. The gate capacitance is a measure of the required charge (supply voltage) to open the transistor, and is calculated as

$$C_{\text{ox}} = \frac{\kappa \cdot \varepsilon_0 \cdot A}{t_{\text{ox}}}.$$

(1.9)

Table 1.2 shows how the different MOSFET parameters can be scaled for a transistor with smaller footprint and similar characteristics. Although the scaling according to this constant electric field principle results in a constant power dissipation density and constant drain current per channel width  $I_d/W$ , the proportional reduction in applied bias and threshold voltage is not desirable. The tradeoff between performance (speed) and power may result in selectively scaling some parameters less rapidly. [1.12]

| paramete             | er                                   | scaling factor |

|----------------------|--------------------------------------|----------------|

| device dimensions    | $t_{\text{OX}}, L, W, x_{\text{j}}$  | 1/α            |

| area                 | A                                    | $1/\alpha^2$   |

| doping concentration | $N_{\mathbf{A}}$                     | α              |

| applied bias         | $V_{\rm ds}, V_{\rm g}, V_{\rm sub}$ | 1/α            |

| current              | $I_{\mathrm{d}}$                     | $1/\alpha$     |

| threshold voltage    | $V_{\rm t}$                          | 1/α            |

| gate capacitance     | $C_{\text{OX}}$                      | 1/α            |

**Table 1.2:** constant electric field scaling factors of MOSFETs. [1.13]

The downscaling of the lateral dimensions of the MOSFET by a factor  $\alpha$ , requires scaling of the oxide thickness by the same factor. Simplified, the scaling of lateral dimensions is limited by photolithography capabilities. Scaling of the oxide thickness, however, is limited by allowed power consumption due to the leakage current through the oxide. Especially when the applied bias is reduced by a smaller factor than the oxide thickness, the limitations of the gate

insulator are approached. Equation 1.9 shows that the dielectric constant is the only device parameter, which can compensate for the reduced oxide thickness.

The gate voltage applied to a MOS structure can be described by

$$V_{\rm G} = V_{\rm fb} + \Phi_{\rm S} + V_{\rm ox} = V_{\rm fb} + \Phi_{\rm S} - \frac{Q}{C_{\rm ox}},$$

(1.10)

where Q is the (gate bias induced) substrate charge per unit area. [1.10] The ratio of substrate charge and oxide capacitance is the potential difference responsible for the substrate charge. The flatband voltage  $V_{\rm fb}$  and surface potential  $\Phi_{\rm S}$  are gate voltage components, required to balance the intrinsic charge in the semiconductor and the potential drop in the substrate, respectively.

The properties of different dielectric materials are commonly presented in relation to their equivalent oxide thickness (EOT), or capacitance equivalent thickness (CET). This normalized parameter is the thickness of a silicon dioxide layer, required to achieve the same gate capacitance. Some publications differentiate between the two parameters, e.g. the CET as extracted from the measured accumulation capacitance, the EOT as effective thickness after compensation for parasitic effects (quantum mechanical, gate depletion, etc.). The method of equivalent thickness determination is, therefore, of importance when comparing results. The *EOT* is basically calculated as

$$EOT = \frac{\kappa_{SiO_2}}{\kappa_{ox}} \cdot t_{ox}, \tag{1.11}$$

in which the dielectric constant of  $SiO_2$  is 3.9. A physically thicker layer of high- $\kappa$  material (a dielectric constant exceeding that of  $SiO_2$ ) is used for the same EOT value, compared to a silicon oxide layer. The equivalent oxide thickness of a new dielectric material is expected to become less than 1.0 nm in 2007 (see table 1.1).

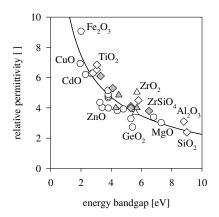

Figure 1.7 shows that the selection of a new dielectric material can not be based on only its dielectric constant. The general trend shows that the permittivity is related to the reciprocal of the energy bandgap. Although the presented permittivity data  $\varepsilon_{\infty}$  is based on the refractive index, the additional ionic polarization component is not expected to invalidate the trend.

## 1.2.4 Qualification for process integration

Three types of dielectric materials (for MOS applications) can be found in literature: ferroelectric materials, polymers and metal oxides (incl. silicon

**Figure 1.7:** correlation between relative permittivity  $\varepsilon_{\infty}$  and energy bandgap  $E_{\rm G}$ . Source of permittivity data: open [1.14] and closed [1.7] symbols; energy bandgap data: circle [1.14], diamond [1.7] and triangle [1.15]. The line represents the relation as proposed by Duffy [1.16].

oxinitrides). The first group contains (Pb,Zr)TiO<sub>3</sub> (PZT), SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> (SBT) and (Ba,Sr)TiO<sub>3</sub> (BST), which are materials with a very high dielectric constant ( $\kappa = 300 \dots 800$ ). Currently, these dielectrics are used in high density DRAM capacitors and nonvolatile ferroelectric RAM (FRAM). In the latter, the extremely high (semi permanent) polarization of the material is used to store data. The relatively new field of organic electronics has gained interest in dielectric polymer materials, but these will be left out of consideration for gate dielectric replacement here, due to its incompatibility with (standard) semiconductor technology. Note, some low- $\kappa$  dielectrics used for interconnect isolation are organic. Metal oxides have lower dielectric constants than the ferroelectric materials, but several are still higher than silicon dioxide.

A fourth group of dielectrics should be mentioned to included special dielectrics, e.g. air, pure water, vacuum and certain gases. Obviously, these dielectrics are not suitable for integration as gate dielectric in integrated circuits. A more appropriate classification scheme for dielectric materials is their dielectric constant. Table 1.3 shows the typical division of the range of dielectric constants. The search for a suitable gate oxide replacement is focused at materials in the third group with a dielectric constant of about 20.

The qualification of a new high- $\kappa$  dielectric is not limited to a suitable dielectric constant and acceptable barrier height for charge tunneling. Requirements of conduction- and valence band offsets are closely related to the energy

|   | dielectric constant   | classification | example(s)                                                               |

|---|-----------------------|----------------|--------------------------------------------------------------------------|

| 1 | $\kappa < 3.9$        | low-κ          | SiLK, TEOS, MSQ                                                          |

| 2 | $3.9 \le \kappa < 10$ | medium-κ       | Si <sub>3</sub> N <sub>4</sub> , Al <sub>2</sub> O <sub>3</sub> , HfSiON |

| 3 | $10 \le \kappa < 100$ | high-κ         | HfO <sub>2</sub> , Ta <sub>2</sub> O <sub>5</sub>                        |

| 4 | $100 \le \kappa$      | super-high-κ   | PZT, SBT, BST                                                            |

**Table 1.3:** classification scheme of dielectric materials.

level of charge in the gate electrode and substrate. It is not unthinkable to engineer a CMOS process with different gate stacks (oxide and gate metal) for NMOS and PMOS transistors. The dielectric material should also have a high breakdown voltage to withstand the large electric fields. Imperfections in the oxide and near the interfaces easily affect the operation of the transistor. Built-in charge, interface trap density and channel mobility are important parameters for the dielectric quality of the oxide.

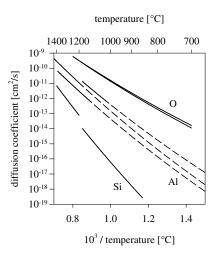

Implementation of a new material requires at least a good adhesion to the other process materials, mainly the silicon substrate and gate material. The thermal stability of the material (in contact with other materials) is of interest. This material property indicates if high temperature process steps during and after deposition of the dielectric, result in interface layer formation, diffusion, crystallization, reduction, silicidation or other undesired effects. Based on available tabulated thermodynamic data, only BeO, MgO and ZrO<sub>2</sub> are thermodynamically stable in contact with silicon at 1000 K. [1.17] For some more binary oxides, insufficient data is available to conclude that they are thermodynamically unstable in contact with silicon at 1000 K. This last group includes the high-κ oxides Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and Re<sub>2</sub>O<sub>3</sub> (Re is a rare earth). Rare earth oxides of interest are Lu<sub>2</sub>O<sub>3</sub>, CeO<sub>2</sub>, Pr<sub>2</sub>O<sub>3</sub>, Tb<sub>2</sub>O<sub>3</sub>, Dy<sub>2</sub>O<sub>3</sub> and Gd<sub>2</sub>O<sub>3</sub>. Table 1.4 shows the periodic table of elements, with the location of elements which have thermodynamically stable binary oxides on silicon.

Table 1.5 shows the elements used in (the most common) high- $\kappa$  binary, ternary and complex oxides. Preferred metals in metal oxides for high- $\kappa$  dielectrics are Y, La, Hf and Zr. Disadvantage of for example Ti and Ta is its reactivity with silicon to form silicides and silicates. Disadvantage of e.g.  $Y_2O_3$  is its high diffusivity of oxygen, which will react with the silicon substrate to form a silicon oxide interface layer. The dielectric should be permeable to hydrogen to allow passivation in surface state anneals, but not to oxygen.

Process integration of the new dielectric material requires the ability to pattern (etch) the material for contact holes. Changing the order of process

| 18    |        | 2 | Не | 10 | Se | 18 | Ar     | 36 | Kr | 54 | Xe | 98 | Rn | 118 | Uno |            |            |              |          |

|-------|--------|---|----|----|----|----|--------|----|----|----|----|----|----|-----|-----|------------|------------|--------------|----------|

| 17    |        |   |    | 6  | ц  | 17 | ت<br>ت | 35 | Br | 53 | П  | 85 | At | 117 | Cus |            |            |              |          |

| 16    |        |   |    | 8  | 0  | 16 | S      | 34 | Se | 52 | Те | 84 | Ъо | 116 | Uuh | 70         | Yb         | 102          | No       |

| 15    |        |   |    | 7  | z  | 15 | Ь      | 33 | As | 51 | Sb | 83 | Bi | 115 | Uup | 69         | Tm         | 101          | Мd       |

| 14    |        |   |    | 9  | C  | 14 | Si     | 32 | Ge | 20 | Sn | 82 | Pb | 114 | Uuq | 89         | Er         | 100          | Fm       |

| 13    |        |   |    | 5  | В  | 13 | A      | 31 | Са | 49 | In | 81 | Ξ  | 113 | Unt | <i>L</i> 9 | Но         | 66           | Es       |

| 12    |        |   |    |    |    |    |        | 30 | Zu | 48 | Cq | 80 | Hg | 112 | Uub | 99         | Dy         | 86           | Ç        |

| 11 12 |        |   |    |    |    |    |        | 29 | Cn | 47 | Ag | 79 | Au | 111 | Rg  | 65         | Tb         | 97           | Bk       |

| 10    |        |   |    |    |    |    |        | 28 | ï  | 46 | Pd | 78 | Pt | 110 | Ds  | 2          | РS         | 96           | Cm       |

| 6     |        |   |    |    |    |    |        | 27 | ပိ | 45 | Rh | 77 | П  | 109 | Mt  | 63         | Eu         | 95           | Am       |

| 8     |        |   |    |    |    |    |        | 26 | Fe | 44 | Ru | 9/ | SO | 108 | Hs  | 62         | Sm         | 94           | Pu       |

| 7     |        |   |    |    |    |    |        | 25 | Mn | 43 | Тс | 75 | Re | 107 | Bh  | 61         | Pm         | 93           | ď        |

| 9     |        |   |    |    |    |    |        | 24 | Cr | 42 | Мо | 74 | ×  | 106 | Sg  | 09         | PΝ         | 92           | n        |

| 5     |        |   |    |    |    |    |        | 23 | >  | 41 | Np | 73 | Та | 105 | Dp  | 59         | Pr         | 91           | Ьa       |

| 4     |        |   |    |    |    |    |        | 22 | Τï | 40 | Zr | 72 | Hf | 104 | Rf  | 58         | ပိ         | 96           | Th       |

| 3     |        |   |    |    |    |    |        | 21 | Sc | 39 | Y  | 71 | Ľ  | 103 | Γι  | 57         | La         | 68           | Ac       |

| 2     |        |   |    | 4  | Be | 12 | Mg     | 20 | Ca | 38 | Sr | 99 | Ba | 88  | Ra  |            | •          |              |          |

| -     |        | 1 | Н  | 3  | Ξ  | 11 | Na     | 19 | ×  | 37 | Rb | 55 | CS | 87  | Fr  | 1          | Lanmanoids | A often oide | chilonas |

| group | period | - | -  | ,  | 7  | ,  | n      | -  | 4  | ų  | n  | 7  | 0  | ı   | ,   | -          | Lar        | •            | Ť        |

**Table 1.4:** elements with (probable) thermodynamically stable binary oxides on silicon at 1000 K, that are acceptable for integration with silicon. [1.17]

| 18    |        | 2 | He | 10 | Ne | 18 | Ar | 36 | Kr | 54 | Xe               | 98 | Rn  | 118 | Uuo         |            |     |           |          |

|-------|--------|---|----|----|----|----|----|----|----|----|------------------|----|-----|-----|-------------|------------|-----|-----------|----------|

| 17    |        |   |    | 6  | Щ  | 17 | C  | 35 | Br | 53 | Ι                | 85 | At  | 117 | Uus         |            |     |           |          |

| 16    |        |   |    | ∞  | 0  | 16 | S  | 34 | Se | 52 | Te               | 84 | Ъ   | 116 | Uuh         | 70         | Yb  | 102       | No<br>No |

| 15    |        |   |    | 7  | Z  | 15 | Ь  | 33 | As | 51 | $^{\mathrm{Sp}}$ | 83 | Bi  | 115 | Uup         | 69         | Tm  | 101       | Md       |

| 14    |        |   |    | 9  | C  | 14 | Si | 32 | Ĝ  | 20 | Sn               | 82 | Pb  | 114 | Uuq         | 89         | Er  | 100       | Fm       |

| 13    |        |   |    | 5  | В  | 13 | Al | 31 | Са | 49 | ln               | 81 | F   | 113 | Uut         | <i>L</i> 9 | Но  | 66        | Es       |

| 12    |        |   |    |    |    |    |    | 30 | Zu | 48 | Cq               | 80 | Hg  | 112 | Uub         | 99         | Dy  | 86        | ŭ        |

| 11 12 |        |   |    |    |    |    |    | 29 | Cn | 47 | Ag               | 79 | Au  | 111 | Rg          | 65         | Tb  | 67        | Bk       |

| 10    |        |   |    |    |    |    |    | 28 | ïZ | 46 | Pd               | 78 | Pt  | 110 | Ds          | 2          | РS  | 96        | Cm       |

| 6     |        |   |    |    |    |    |    | 27 | ပိ | 45 | Rh               | 77 | lr. | 109 | Mt          | 63         | En  | 95        | Am       |

| 8     |        |   |    |    |    |    |    | 56 | Ъе | 44 | Ru               | 92 | o   | 108 | Hs          | 62         | Sm  | 94        | Pu       |

| 7     |        |   |    |    |    |    |    | 25 | Mn | 43 | Тс               | 75 | Re  | 107 | Bh          | 61         | Pm  | 93        | aN       |

| 9     |        |   |    |    |    |    |    | 24 | Cr | 42 | Mo               | 74 | ×   | 106 | $_{\rm gc}$ | 09         | PΝ  | 92        | n        |

| 5     |        |   |    |    |    |    |    | 23 | >  | 41 | Np               | 73 | Та  | 105 | Db          | 59         | Pr  | 91        | Pa       |

| 4     |        |   |    |    |    |    |    | 22 | Ξ  | 40 | Zr               | 72 | Hf  | 104 | Rf          | 58         | ce  | 06        | T        |

| 3     |        |   |    |    |    |    |    | 21 | Sc | 39 | Y                | 71 | ŗ   | 103 | Lr          | 57         | La  | 68        | Ac       |

| 2     |        |   |    | 4  | Be | 12 | Mg | 20 | Ca | 38 | Sr               | 99 | Ba  | 88  | Ra          |            |     |           |          |

| 1     |        | 1 | Н  | 3  | Ë  | 11 | Na | 19 | X  | 37 | Rb               | 55 | C   | 87  | Fr          | anthanoids |     | Actinoids |          |

| group | period | - | -  | ,  | 7  | 3  |    | -  | 1  | ų  | c                | 9  |     | 7   |             | -          | Lar | ACI       |          |

**Table 1.5:** elements of most high-κ binary oxides: Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, La<sub>2</sub>O<sub>5</sub>, La<sub>2</sub>O<sub>3</sub> [1.15]; CeO<sub>2</sub> [1.18]; Pr<sub>2</sub>O<sub>3</sub> [1.19]; Gd<sub>2</sub>O<sub>3</sub> [1.20, 1.21]; Tm<sub>2</sub>O<sub>3</sub>, Nd<sub>2</sub>O<sub>3</sub>, Sm<sub>2</sub>O<sub>3</sub>, Eu<sub>2</sub>O<sub>3</sub>, Ho<sub>2</sub>O<sub>3</sub>, Ho<sub>2</sub>O<sub>3</sub>, Er<sub>2</sub>O<sub>3</sub> [1.22, 1.23].

| 18    |        | 2 | He | 10 | Se | 18  | Ar     | 36 | Kr | 54 | Xe | 98 | Rn | 118 | Uno |            |            |         |             |  |

|-------|--------|---|----|----|----|-----|--------|----|----|----|----|----|----|-----|-----|------------|------------|---------|-------------|--|

| 17    |        |   |    | 6  | ц  | 17  | ت<br>ت | 35 | Br | 53 | П  | 85 | At | 117 | Uus |            |            |         |             |  |

| 16    |        |   |    | 8  | 0  | 16  | S      | 34 | Se | 52 | Те | 84 | Ро | 116 | Uuh | 70         | Yb         | 102     | No          |  |

| 15    |        |   |    | 7  | z  | 15  | Ь      | 33 | As | 51 | Sb | 83 | Bi | 115 | Uup | 69         | Tm         | 101     | Md          |  |

| 14    |        |   |    | 9  | C  | 14  | Si     | 32 | Ge | 50 | Sn | 82 | Pb | 114 | Uuq | 89         | Ë          | 100     | Fm          |  |

| 13    |        |   |    | 5  | В  | 13  | Al     | 31 | Ga | 49 | ln | 81 | E  | 113 | Uut | <i>L</i> 9 | Но         | 66      | Es          |  |

| 12    |        |   |    |    |    |     |        | 30 | Zu | 48 | р  | 80 | Hg | 112 | Unb | 99         | Dy         | 86      | Ç           |  |

| 11    |        |   |    |    |    |     |        | 59 | Cn | 47 | Ag | 79 | Au | 111 | Rg  | 65         | Tb         | 26      | Bk          |  |

| 10    |        |   |    |    |    |     |        | 28 | ïZ | 46 | Pd | 78 | Pt | 110 | Ds  | 2          | РS         | 96      | Cm          |  |

| 6     |        |   |    |    |    |     |        | 27 | ပိ | 45 | Rh | 11 | П  | 109 | Mt  | 63         | En         | 95      | Am          |  |

| 8     |        |   |    |    |    |     |        | 56 | Еe | 44 | Ru | 9/ | o  | 108 | Hs  | 62         | Sm         | 94      | Pu          |  |

| 7     |        |   |    |    |    |     |        | 25 | Mn | 43 | Tc | 75 | Re | 107 | Bh  | 61         | Pm         | 93      | Np          |  |

| 9     |        |   |    |    |    |     |        | 24 | Cr | 42 | Mo | 74 | A  | 106 | Sg  | 09         | ρN         | 92      | D           |  |

| 5     |        |   |    |    |    |     |        | 23 | >  | 41 | γp | 73 | Та | 105 | Db  | - 65       | Pr         | 91      | Pa          |  |

| 4     |        |   |    |    |    |     |        | 22 | Ϊ  | 40 | Zr | 72 | Hf | 104 | Rf  | 58         | రి         | 06      | Th          |  |

| 3     |        |   |    |    |    |     |        | 21 | Sc | 39 | Y  | 71 | Ľ  | 103 | Lr  | 57         | La         | 68      | Ac          |  |

| 2     |        |   |    | 4  | Be | 12  | Mg     | 20 | Ca | 38 | Sr | 99 | Ba | 88  | Ra  |            | •          |         |             |  |

| -     |        | 1 | Н  | 3  | Ľ  | 11  | Na     | 19 | ×  | 37 | Rb | 55 | C  | 87  | Ή   | 1          | Lanmanoids | dionite | Actillolius |  |

| group | period | - | -  | 2  |    | 3 8 |        | 4  |    | 5  |    | 9  |    | 7   |     | _          | Lan        |         | Ac          |  |

**Table 1.6:** elements of some reported epitaxial high- $\kappa$  oxides on Si(001): Al<sub>2</sub>O<sub>3</sub> [1.24,1.25]; Y-stabilized ZrO<sub>2</sub> (YSZ), Y-stabilized HfO<sub>2</sub> (YSH) [1.26]; Y<sub>2</sub>O<sub>3</sub> [1.27], CeO<sub>2</sub>, Pr<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub> [1.28].

steps or selective deposition of the gate stack are less trivial solutions. One important and undesired property of high- $\kappa$  gate dielectrics is the (apparent intrinsic) reduction of inversion layer mobility. This issue has been reported to be due to fixed charge at the  $Al_2O_3/SiO_x$  interface, which induces Coulomb scattering. [1.29, 1.30] Other explanations have been found in Coulomb interaction of electrons in the channel with electrons in the depletion layer of the gate [1.31], dopant (boron) diffusion into the oxide [1.32] and remote phonon coupling to inversion layer charge. [1.33] A second issue is the so-called Fermi level pinning at the poly-Si/high- $\kappa$  interface due to metal-silicon bonds [1.34], which effectively results in the polysilicon gate to be replaced by different metal gates for NMOS and PMOS devices.

Finally, epitaxial layers are of interest because of its control of defect chemistry, chemical stability, higher channel mobility and low interface trap density. Table 1.6 shows the elements of high- $\kappa$  dielectric materials, which have been reported to be epitaxially deposited on Si(001). Materials that are suitable for epitaxial growth are "silicon derived" oxides and perovskites: materials with a small lattice mismatch with silicon.

## 1.3 Deposition techniques

Although thermal oxidation may still be used to fully oxidize deposited thin metal layers, replacement of  $SiO_2$  by a high- $\kappa$  dielectric will introduce new process techniques to the semiconductor technology. Deposition of gate dielectrics in the front-end of the process is a more critical step than deposition of metal interconnects in the back-end of the process. The requirements of uniformity and thickness control, step coverage and defect density will exceed that of traditional thermal oxidation.

Clearly, not all deposition techniques are suitable to deposit thin gate dielectric films. Some of the disqualifying factors are restrictions of the thermal budget, excess of energy of the deposited material and inherent contamination. Two deposition techniques will be briefly discussed in the following sections: pulsed laser deposition and atomic layer deposition. Chapters 2 and 3 include more detailed discussions and results obtained with these two techniques.

## 1.3.1 Pulsed laser deposition

The pulsed laser deposition (PLD) technique is a vapor deposition method, in which a laser is used to evaporate the source material. The pulsed laser beam

creates a dense vapor layer of target material on the target surface. The vapor absorbs most of the energy in the laser pulse and is transformed to an energetic plasma. The plasma will expand due to the pressure and temperature gradients, and a plume is formed of a characteristic shape. By placing a substrate inside or near the plume of evaporated material, condensation of source material can occur. The plasma is very reactive with  $O_2$  in the chamber, thus the deposition ambient affects the deposited material.

The first use of laser energy to evaporate material and deposit thin films (in a vacuum system) was already reported in 1965. [1.35] Continued research resulted in numerous publications on successful deposition of oxides, semi-conductors and superconductors. [1.36] Although the versatility of the PLD technique has been gratefully used in material science, semiconductor industry has not yet employed this technique in its production process.

Thin epitaxial layers can be deposited by PLD, but this depends on substrate quality and particle kinetics. Advantage of PLD is its ability to (locally) deposit exactly 1 unit cell, under the right process conditions, resulting in a smooth surface. Deposition of a metal oxide material is possible by using a metal target and an oxygen ambient. Single crystalline target materials result in a higher quality deposited layer, because of a lower impurity density in the target. To avoid craters in the target surface, the laser beam is scanned across the surface or the target is rotated. Typical specifications of commercially available excimer lasers are pulses of 20 ns, frequencies up to 100 Hz and a pulse energy up to 700 mJ. [1.37]

## 1.3.2 Atomic layer deposition

Growth by atomic layer deposition chemistry, using metal chlorides and water vapor, was first reported by Aleskovskii in 1965. [1.38] Since then, three different names have been used in literature for (more or less) the same deposition technique: atomic layer chemical vapor deposition (ALCVD<sup>TM</sup>), atomic layer deposition (ALD) and atomic layer epitaxy (ALE). The latter is sometimes misused when the deposited material is not an epitaxial layer. The abbreviation for atomic layer chemical vapor deposition has been trademarked by ASM International. Therefore, atomic layer deposition has now become the preferred name for the deposition technique.

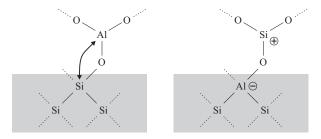

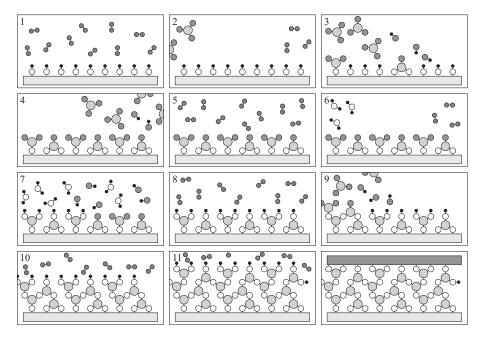

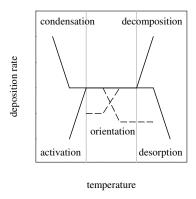

The ALD process of metal oxides is based on the sequential exposure to oxidizing and reducing precursor vapors. The precursor molecules, e.g. the reducing ones, saturate the surface by chemisorption. This process is limited

by the amount of suitable, available and accessible bonding sites. A second precursor is used as an oxidizing agent, removing ligands of the first precursor molecules on the surface and creating new bonding sites for the first precursor. Successful layer-by-layer growth is achieved by sequential repetition of both steps and avoiding gas phase reactions between both precursors. The deposition rate, or growth-per-cycle, is considered to be constant during the deposition of the layer (except for the initial coverage of the sublayer). The deposition is not sensitive to gas purge times, as long as they are long enough to saturate the surface.

#### 1.4 Alternative solutions

Numerous techniques are available to deposit materials on a substrate. None of them can match the simplicity of thermal oxidation of silicon to form silicon oxide. Low pressure CVD, plasma enhanced CVD and sputtering techniques are widely used for other process steps in the semiconductor technology. Although a CVD process might exist for deposition of the high- $\kappa$  material, the thickness and uniformity requirements of the gate oxide are generally not met. The formation of metal oxides by sputtering a thin metal layer and subsequent oxidation, has been published and shows promising results. However, the bombardment of the substrate by high energetic particles results in a mobility reduction by defects and subsurface implanted metal atoms.

The need of a new gate oxide for CMOS technology, is also a motivation for research on completely different solutions for logic circuitry. Prefixed by the scientific buzzword "nano", several new techniques to operate digital information have been presented. Examples of futuristic transistors include optical switches, single electron transistors [1.39] and carbon nano-tubes. [1.40] However, it will take years (and years if at all) before multimillion transistor circuits can be manufactured with sufficient reliability. The current state of this research is still the development of full functionality of a single transistor.

A change in geometry of CMOS structures (e.g. vertical structures [1.41] or dual gate devices) might solve or suspend some of the barriers of down-scaling, and is more easily utilized by the semiconductor industry. Although alternative structures are not directly a solution to the gate dielectric problem, the change in electric field might be an advantage for the implementation of high-κ dielectrics.

# 1.5 Conclusions

The development of semiconductor technology has reached several barriers in the downscaling trend of conventional CMOS transistors. A solution for the high leakage current of nanometer thick silicon oxide layers can be found in replacement by a high- $\kappa$  dielectric material. Up to now, no combination of material and process has been found to match the electrical properties of thermally oxidized silicon and be suitable for full integration into the semi-conductor technology. Although a long list of requirements and preferences is easily formed, the realization of an alternative process to create a suitable gate oxide appears to be very difficult.

#### References

- [1.1] ITRS, International technology roadmap for semiconductors, available online, http://public.itrs.net/, 1999-2005.

- [1.2] Buchanan D.A., "Scaling the gate dielectric: Materials, integration, and reliability", *IBM Journal of Research and Development*, vol. 43, pp. 245–264, 1999.

- [1.3] Wallace R.M. and Wilk G.D., "Exploring the limits of gate dielectric scaling", Semiconductor International, vol. 24, no. 6, pp. 153–158, 2001.

- [1.4] Kasap S.O., Principle of Electronic Materials and Devices, McGraw-Hill, New York, 3rd edition, 2006

- [1.5] Cheng D.K., Field and Wave Electromagnetics, Addison-Wesley Publishing Company, Reading (Massachusetts), 2nd edition, 1989.

- [1.6] Atkins P.W., *Physical Chemistry*, Oxford University Press, Oxford, 6th edition, 2001.

- [1.7] Robertson J., "Band offsets of high dielectric constant gate oxides on silicon", *Journal of Non-Crystalline Solids*, vol. 303, pp. 94–100, 2002.

- [1.8] Ludeke R., Cuberes M.T., and Cartier E., "Local transport and trapping issues in Al<sub>2</sub>O<sub>3</sub> gate oxide structures", Applied Physics Letters, vol. 76, pp. 2886–2888, 2000.

- [1.9] Braun D., "Electronic injection and conduction processes for polymer devices", *Journal of Polymer Science B*, vol. 41, pp. 2622–2629, 2003.

- [1.10] Schroder D.K., Semiconductor material and device characterization, John Wiley & Sons, New York, 2nd edition, 1998.

- [1.11] Depas M., Vermeire B., Mertens P.W., van Meirhaeghe R.L., and Heyns M.M., "Determination of tunnelling parameters in ultra-thin oxide layer poly-Si/SiO<sub>2</sub>/Si structures", *Solid-State Electronics*, vol. 38, pp. 1465–1471, 1995.

- [1.12] Davari B., Dennard R.H., and Shahidi G.G., "CMOS scaling for high performance and low power - The next ten years", *Proceedings of the IEEE*, vol. 83, pp. 595–606, 1995.

- [1.13] Dennard R.H., "Design of ion-implanted MOSFET's with very small physical dimensions", IEEE Journal of Solid-State Circuits, vol. Sc-9, pp. 256–268, 1974.

- [1.14] Dimitrov V. and Sakka S., "Electronic oxide polarizability and optical basicity of simple oxides", Journal of Applied Physics, vol. 79, pp. 1736–1740, 1996.

- [1.15] Wilk G.D., "High-κ gate dielectrics: Current status and materials properties consideration", *Journal of Applied Physics*, vol. 89, pp. 5243–5275, 2001.

- [1.16] Duffy J.A., "Chemical bonding in the oxides of the elements: a new appraisal", *Journal of Solid State Chemistry*, vol. 62, pp. 145–157, 1986.

- [1.17] Hubbard K.J. and Schlom D.G., "Thermodynamic stability of binary oxides in contact with silicon", Journal of Materials Research, vol. 11, pp. 2757–2776, 1996.

- [1.18] Khodan A.N., Contour J.-P., Michel D., Durand O., Lyonnet R., and Mihet M., "ZrO<sub>2</sub>-CeO<sub>2</sub> and CeO<sub>2</sub>-La<sub>2</sub>O<sub>3</sub> film growth on oxide substrates and their applications in oxide heterostructures", *Journal of Crystal Growth*, vol. 209, pp. 828–841, 2000.

- [1.19] Osten H.J., Bugiel E., and Fissel A., "Epitaxial praseodymium oxide: a new high-K dielectric", Solid-State Electronics, vol. 47, pp. 2161–2165, 2003.

- [1.20] Kwo J., Hong M., Kortan A.R., Queeney K.T., Chabal Y.J., Mannaerts J.P., Boone T., Krajewski J.J., Sergent A.M., and Rosamilia J.M., "High ε gate dielectrics Gd<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> for silicon", *Applied Physics Letters*, vol. 77, pp. 130–132, 2000.

- [1.21] Kwo J., Hong M., Kortan A.R., Queeney K.L., Chabal Y.J., Opila R.L., Muller D.A., Chu S.N.G., Sapjeta B.J., Lay T.S., Mannaerts J.P., Boone T., Kwautter H.W., Krajewski J.J., Sergent A.M., and Rosamilia J.M., "Properties of high κ gate dielectrics Gd<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> for Si", *Journal of Applied Physics*, vol. 89, pp. 3920–3927, 2001.

- [1.22] Ohmi S., Akama S., Kikuchi A., Kashiwagi I., Ohshima C., Taguchi J., Yamamoto H., Kobayashi C., Sato K., Takeda M., Oshima K., Ishiwara H., and Iwai H., "Rare earth metal oxide gate thin films prepared by E-beam deposition", *IEEE International Workshop on Gate Insulator*, pp. 200–204, 2001.

- [1.23] Päiväsaari J., Putkonen M., and Niinistö L., "A comparative study on lanthanide oxide thin films grown by atomic layer deposition", *Thin Solid Films*, vol. 472, pp. 275–281, 2005.

- [1.24] Kimura T. and Ishida M., "Development of surface morphology of epitaxial Al<sub>2</sub>O<sub>3</sub> on silicon by controlling reaction between oxygen and silicon surface", *Japanese Journal of Applied Physics*, vol. 38, pp. 853–856, 1999.

- [1.25] Whangbo S.W., Choi Y.K., Chung K.B., Jang H.K., and Whang C.N., "Epitaxial growth of Al<sub>2</sub>O<sub>3</sub> thin films on Si(100) using ionized beam deposition", *Journal of Vacuum Science and Technology A*, vol. 19, pp. 410–413, 2001.

- [1.26] Dai J.Y., Lee P.F., Wong K.H., Chan H.L.W., and Choy C.L., "Epitaxial growth of yttrium-stabilized HfO<sub>2</sub> high-k gate dielectric thin films on Si", *Journal of Applied Physics*, vol. 94, pp. 912–915, 2003.

- [1.27] Dimoulas A., Travlos A., Vellianitis G., Boukos N., and Argyropoulos K., "Direct heteroepitaxy of crystalline Y<sub>2</sub>O<sub>3</sub> on Si(001) for high-k gate dielectric applications", *Journal of Applied Physics*, vol. 90, pp. 4224–4230, 2001.

- [1.28] Lettieri J., Haeni J.H., and Schlom D.G., "Critical issues in the heteroepitaxial growth of alkalineearth oxides on silicon", *Journal of Vacuum Science and Technology A*, vol. 20, pp. 1332–1340, 2002.

- [1.29] Hiratani M., Torii K., Shimamoto Y., and Saito S., "Built-in interface in high-k gate stacks", Applied Surface Science, vol. 216, pp. 208–214, 2003.

- [1.30] Torii K., Shimamoto Y., Saito S., Obata K., Yamauchi T., Hisamoto D., Onai T., and Hiratani M., "Effect of interfacial oxide on electron mobility in metal insulator semiconductor field effect transistors with Al<sub>2</sub>O<sub>3</sub> gate dielectrics", *Microelectronic Engineering*, vol. 65, pp. 447–453, 2003.

- [1.31] Fischetti M.V., "Long-range Coulomb interactions in small Si devices. Part II. Effective electron mobility in thin-oxide structures", *Journal of Applied Physics*, vol. 89, pp. 1232–1250, 2001.

- [1.32] Chang C.-Y., Chen C.-C., Lin H.-C., Liang M.-S., Chien C.-H., and Huang T.-Y., "Reliability of ultrathin gate oxides for ULSI devices", *Microelectronics Reliability*, vol. 39, pp. 553–566, 1999.

- [1.33] Chau R., Datta S., Doczy M., Doyle B., Kavalieros J., and Metz M., "High-k/metal-gate stack and its MOSFET characteristics", *IEEE Electron Device Letters*, vol. 25, pp. 408–410, 2004.

- [1.34] Hobbs C., Fonseca L., Dhandapani V., Samavedam S., Tayor B., Grant J., Dip L., Triyoso D., Hegde R., Gilmer D., Garcia R., Roan D., Lovejoy L., Rai R., Hebert L., Tseng H., White B., and Tobin P., "Fermi level pinning at the polySi/metal oxide interface", *IEEE Symposium on VLSI Technology*, pp. 9–10, 2003.

- [1.35] Smith H.M. and Turner A.F., "Vacuum deposited thin firms using a ruby laser", *Applied Optics*, vol. 4, pp. 147–148, 1965.

- [1.36] Cheung J.T. and Sankur H., "Growth of thin films by laser-induced evaporation", CRC Critical Reviews in Solid State and Material Sciences, vol. 15, pp. 63–109, 1988.

- [1.37] Lambda Physik, COMPexPro product specifications, available online, http://www.lambdaphysik.com/, 2005.

- [1.38] Shevjakov A.M., Kuznetsova G.N., and Aleskovskii V.B., Proceedings of 2nd USSR conference on high-temperature chemistry of oxides, Leningrad, 1965, in: Khim. Vysokotemp. Mater., Nauka, Leningrad, 1967.

- [1.39] Chou S.Y. and Wang Y., "Single-electron Coulomb blockade in a nanometer field-effect transistor with a single barrier", Applied Physics Letters, vol. 61, pp. 1591–1593, 1992.

- [1.40] Tans S.J., Verschueren A.R.M., and Dekker C., "Room-temperature transistor based on a single carbon nanotube", *Nature*, vol. 393, pp. 49–51, 1998.

- [1.41] Masahara M., Matsukawa T., Ishii K., Liu Y., Nagao M., Tanoue H., Tanii T., Ohdomari I., and Kanemaru S., "Fabrication of ultrathin Si channel wall for vertical double-gate metal-oxidesemiconductor field-effect transistor (DG MOSFET) by using ion-bombardment-retarded etching (IBRE)", Japanese Journal of Applied Physics, vol. 42, pp. 1916–1918, 2003.

| In-situ RHEED and characterization of ALD Al <sub>2</sub> O <sub>3</sub> gate dielectrics |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

|                                                                                           |  |  |  |

# 2 Pulsed laser deposition

A deposition technique is a process in which material is removed from a reservoir and applied to a sample. The energy, required for controlled transportation of the material, can be supplied in various ways from various sources. The result should be a layer of specified thickness, uniformity, composition, roughness, stability, ..., and any other preferred layer or material property. The intrinsic properties are usually only known for the bulk material and are difficult to replicate in deposited thin films. Deposition techniques are complicated processes with numerous interrelated parameters that all affect the final result.

#### 2.1 Introduction

Pulsed laser deposition (PLD) has become an interesting technique for (high- $\kappa$ ) material research, due to its flexible use of multiple target materials and ability to deposit epitaxial layers. The use of an external laser as energy supply allows reduction of the reactor volume and avoids a possible source of contamination, e.g. sputter guns or filaments in evaporation systems.

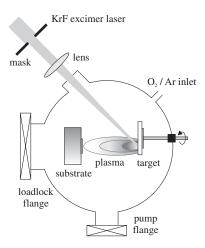

A laser beam is focussed by lenses to a sufficiently high energy density to evaporate target material. The laser spot creates a dense vapor layer of target material in front of the target surface. [2.1] This vapor absorbs most of the energy of the laser pulse and is transformed to an energetic plasma of target material. The plasma will expand due to the pressure gradient and a plume is formed of a characteristic shape. A substrate can be placed near or inside the plume of excitated material to deposit a layer of the evaporated material. Figure 2.1 shows a schematic drawing of a PLD system.

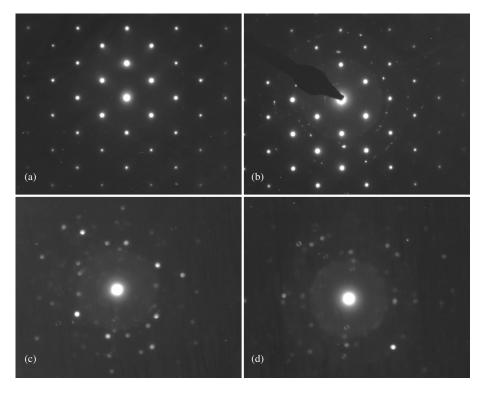

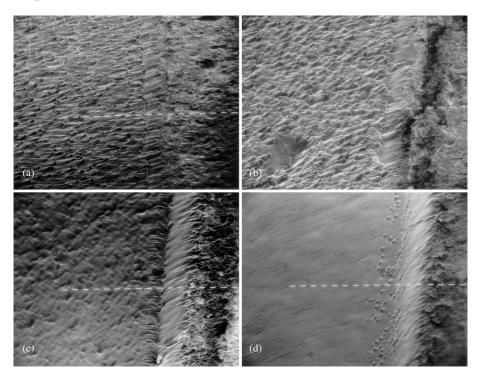

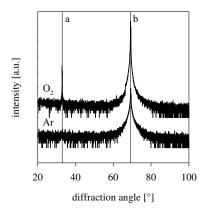

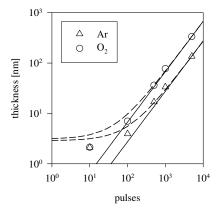

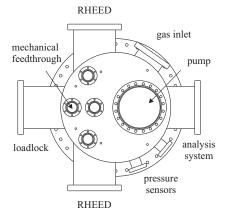

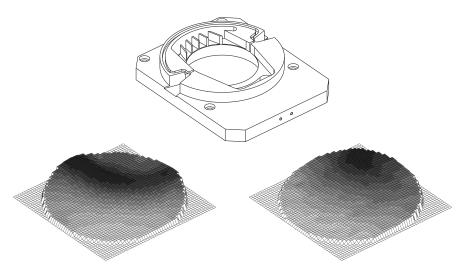

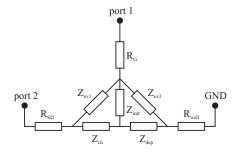

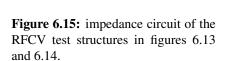

Figure 2.1: schematic drawing of the PLD system.